我仔细阅读了一下DT930F+的电路图,同时也参看了其他几种基于ICL7129的手持四位半的电路图,有几个在电路上的设计我不是很理解,所以来请教一下各位大神。

1、根据别的双积分AD工作过程推测,参考电容(Reference Capacitor)在积分(Integrate)和反积分(De-Integrate)阶段是悬空的并在若干反积分阶段放电,在零积分(Zero-Integrate)和栓锁(Latch)阶段充电。那么这参考电容在反积分阶段会放多少电呢,会不会放净?而在充电过程中又需要多大的充电电流,也就是会从电压基准吸取多大的电流呢?而充电时,对于电压基准源来说,这是不是一个较大的容性负载?

2、在美信ICL7129的手册里,关于参考电容是这样说的,在多数情况下,REF LO输入端连接到Common端,REF HI输入端高于Common端1V。在积分和空闲阶段(Integration and idle phases)参考电容被连接到参考输入端(CREF+ 接 REF HI,CREF- 接 REF LO)。在积分阶段,一个负输入信号将使积分器输出为正,ICL7129A/MAX7129数字部分在反积分阶段会将Cref+端连接到Common。既然Cref-端在积分阶段也是连接在Common端,那么在积分阶段到反积分阶段转变期间CREF端的电压就保持不变。但是如果积分阶段的输入信号为正,ICL7129A/MAX7129的数字部分将会把Ref Cap+端连接到Common。在此情况下,参考电容的两端同时向负方向移动1V,即电位同时降低1V。在参考电容端子上的任何杂散电容也会在进行1V移动时充电,从而减小参考电容上的电压,使比例因子改变。这种称为“翻转误差”的误差可由使用1μF或更大的参考电容来降低到1个读数以下。而我看到的那几个四位半电路中,参考电容都是0.1μF的,为什么会使用这样小的参考电容呢?这会不会真的使表有较大的翻转误差,比如1个字以上,有没有方便试一下的大神,看看自己手上的表翻转误差有多少?我简单测试了一下我的DT930FD,貌似有几个字的翻转误差,不知道是没测好还是真的这样。(关于参考电容何时充电,手册没有明确指出,但是有一些不完整的描述,可是似乎有些矛盾。前面说“The reference capacitor must be a low leakage capacitor since it stores the reference voltage while floating during both the integrate and De-integrate phases.”后面又说“During the Integration and idle phases the reference capacitor is connected to the Reference Inputs (CREF+ to Ref Hi and CREF- to Ref Lo).)

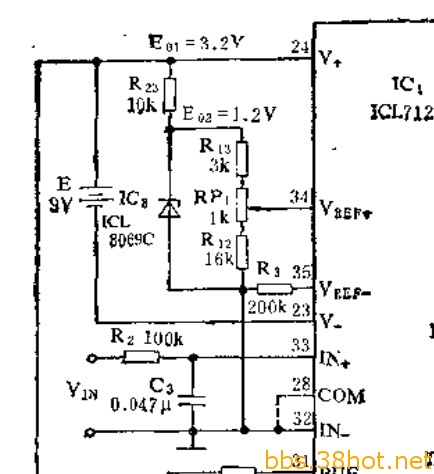

3、这个是关于基准电压的。在930的电路中7129的参考输入负端(REF LO)之前串联了一个200kΩ的电阻,别的表中或多或少也会有这样一个电阻,但手册推荐的电路中并没有这个电阻,串联这个电阻的目的是什么?这个电阻看起来似乎完全没必要的啊。

图:DT930F+电压基准部分

多谢各位的解答!! |