本帖最后由 forester 于 2015-11-4 16:52 编辑

今天无聊,看了一下34410和3458的ADC,突然发现二者非常相像。

这些电路都是为了高速积分做准备的。因此发贴问一下各位大神,这是ADC吗?(水平有限,以下全部为猜测,不对之处请指正)。

首先看34410的ADC,基准和34401一样,是交替接入的。那么问题来了,如果在53M的时钟下,进行基准切换,普通的模拟开关已经不能胜任了。下面是常用模拟开关对比:

| ID | Type | Vin(V) | Ron(Ω) | △Ron(Ω) | Ton(nS) | Ieakage(nA) | Supply(V) | Digital Section | | MAX333 | SPDT | 20 | 35 | 1 | 175 | 1 | 30-40 | TTL,CMOS | | 74HC4053 | SPDT | 12 | 280 | 40 | 550 | 1000 | 12 | CMOS |

再来看34401的解决办法:

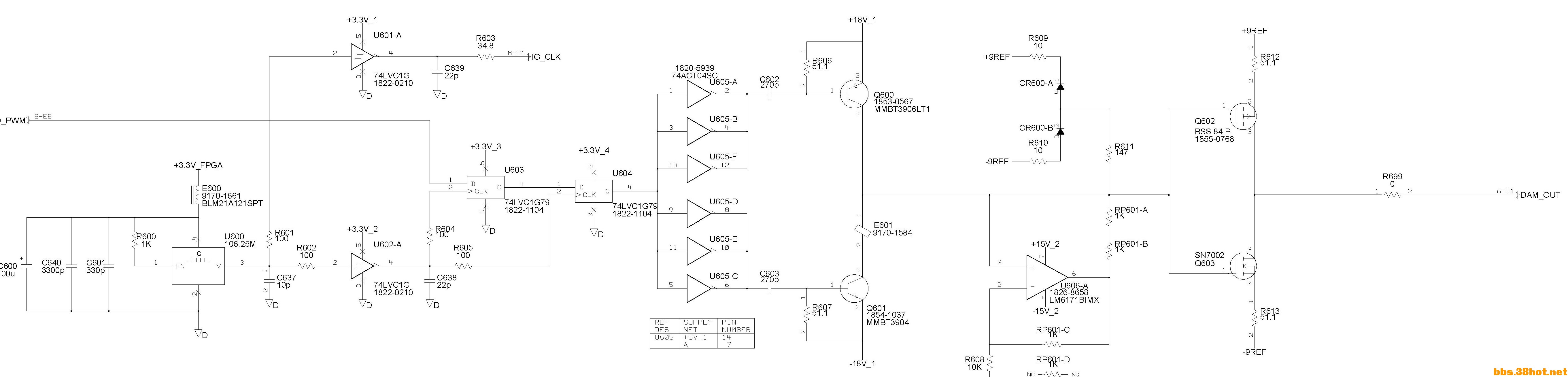

106.25M的时钟,一路做为CPLD的主时钟源,另一路用二个D触发器,把基准切换信号打二拍,消除毛刺,信号进入二个三并连的六反相器,提高驱动能力,驱动二个250M FT的双极型晶体管,实现对基准的高速切换,二个270P电容的存在,使得电路永远不会出现晶体管在暂稳态时同时接通的情况。产生DAM_OUT通过20K电阻进入积分器。

34410ADC

AC_OUT、DC_OUT、DAM_OUT通过一个网络电阻进入积分器。分别为30K、50K、20K。

AC和DC相对于基准电阻的比例分别为:1.5和2.5。

积分器为OP27和BJT超高速运放AD829组成(3458用的是AD844,都是200V/us左右的SR)复合运放,以提高压摆率,实现超高速测量。

这个复合运放有一个缺点,就是输入偏置电流太高,如果采用BFET输入运放,又没有高的压摆率。

因此,引入Q504,用于V-I和I-V转换,从而避免了输入偏置电流的影响。

如果直接短路这只JFET,那么电路就和34401一样,但积分电容变成了47P。

最后为比较电路,34410已经不用比较器或原来的COMS电平比较器,而是用了一只80M SPS的8位ADC做为积分“过零”检测电路,同实实现乘余电荷的测量。

另一只10位20M SPS的ADC作用我不太理解。

由FPGA产生解发信号,解发二片超高速ADC进行AD转换。

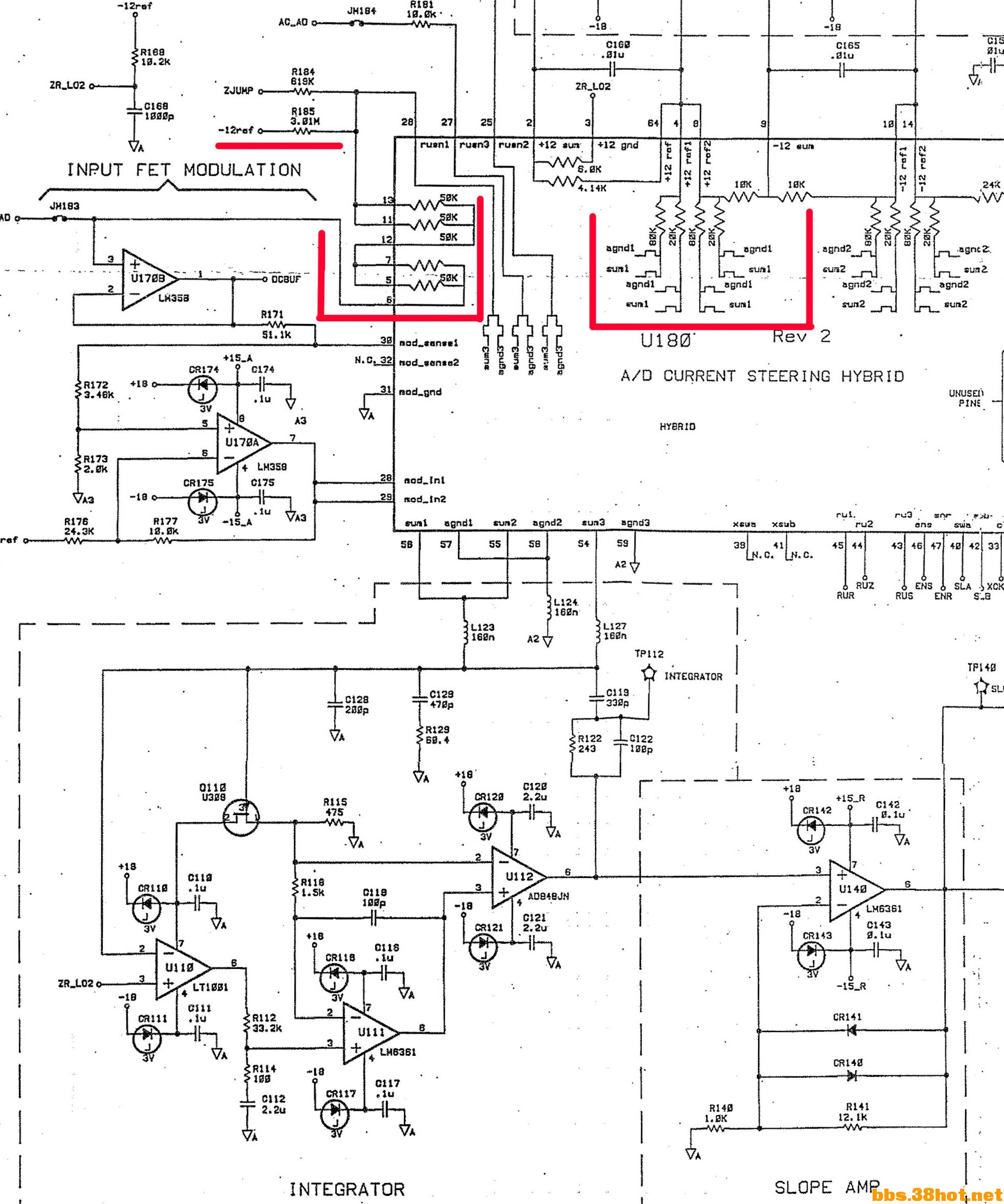

上面是3458的ADC,和34410基本上是一样的架构,但是检零部分用的还是通用积分ADC的检零电路,画红线的地方为积分电阻。AC为10K,DC为50K,多余部分为20K、80K、3.01M组合。积分运放用的是AD844,也是超高速运放,积分电容为100P,接法和34401有点差别。3.01M电阻用于测量20K和80K快速斜率时,检零过冲电荷。

还有个疑问,3458号称41/2位时(16比特)100,000读数/s。换算成计数需要6G,在34410j里面。因为有10位20M SPS流水线ADC测低位。高位积分ADC只需要6个计数就可以实现16位分辨率了。但3458有一个这样的ADC吗?

以上分析纯属猜测,我自己都信

|