该电压源历经 V0.1 原理验证手工版、V0.3 原理验证工厂 PCB,如今是 V1.0 长期可行性验证 PCB,因为还是一个出于验证的 PCB 和电路,因此有很多不完善甚至匪夷所思(应该用双运放的,某人因为偷懒用了 4 运放,生生浪费掉两个)的地方,敬请谅解。

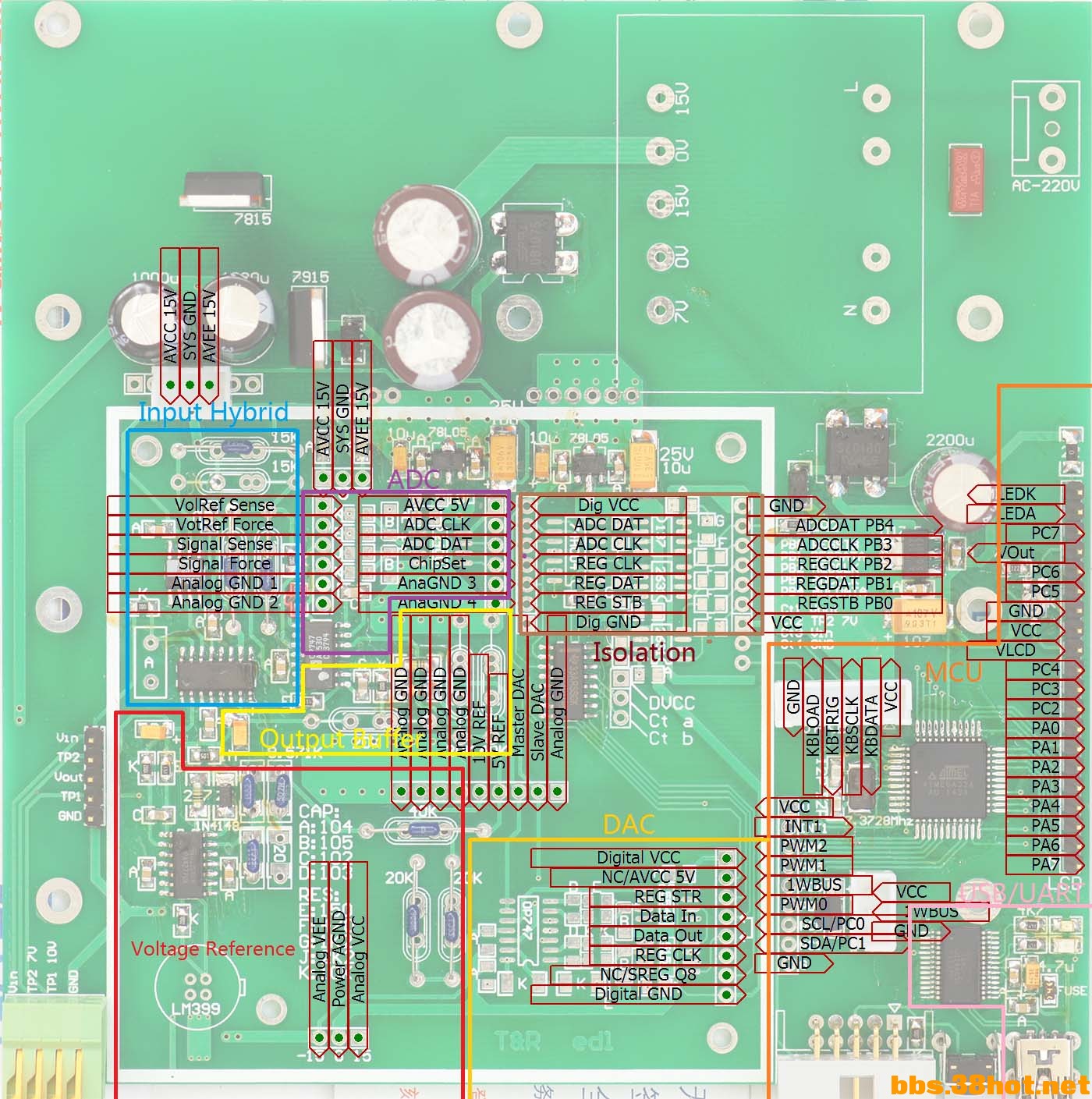

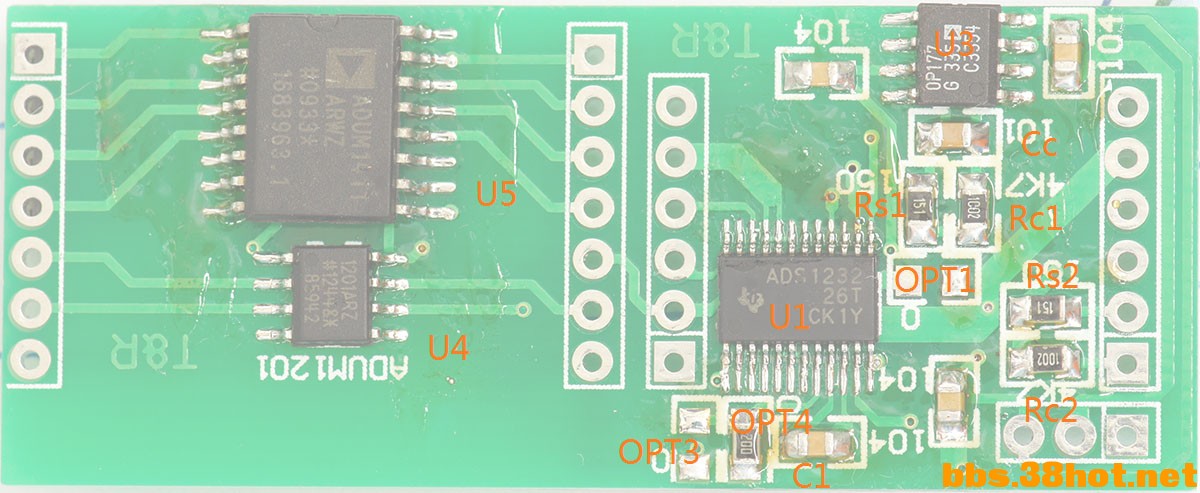

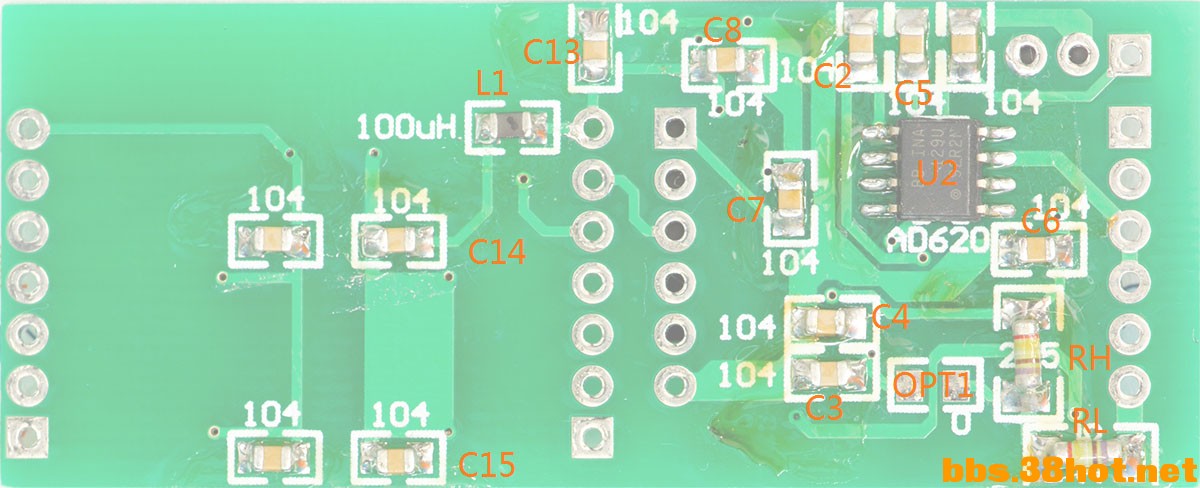

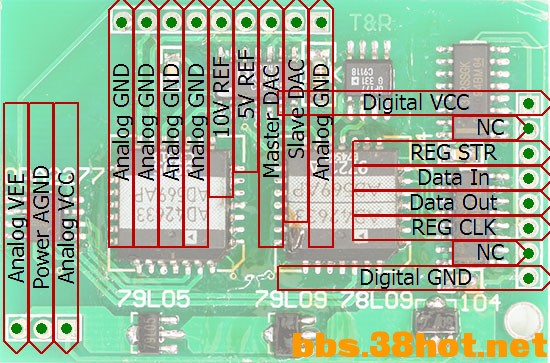

主板功能区域区分和接口配置:

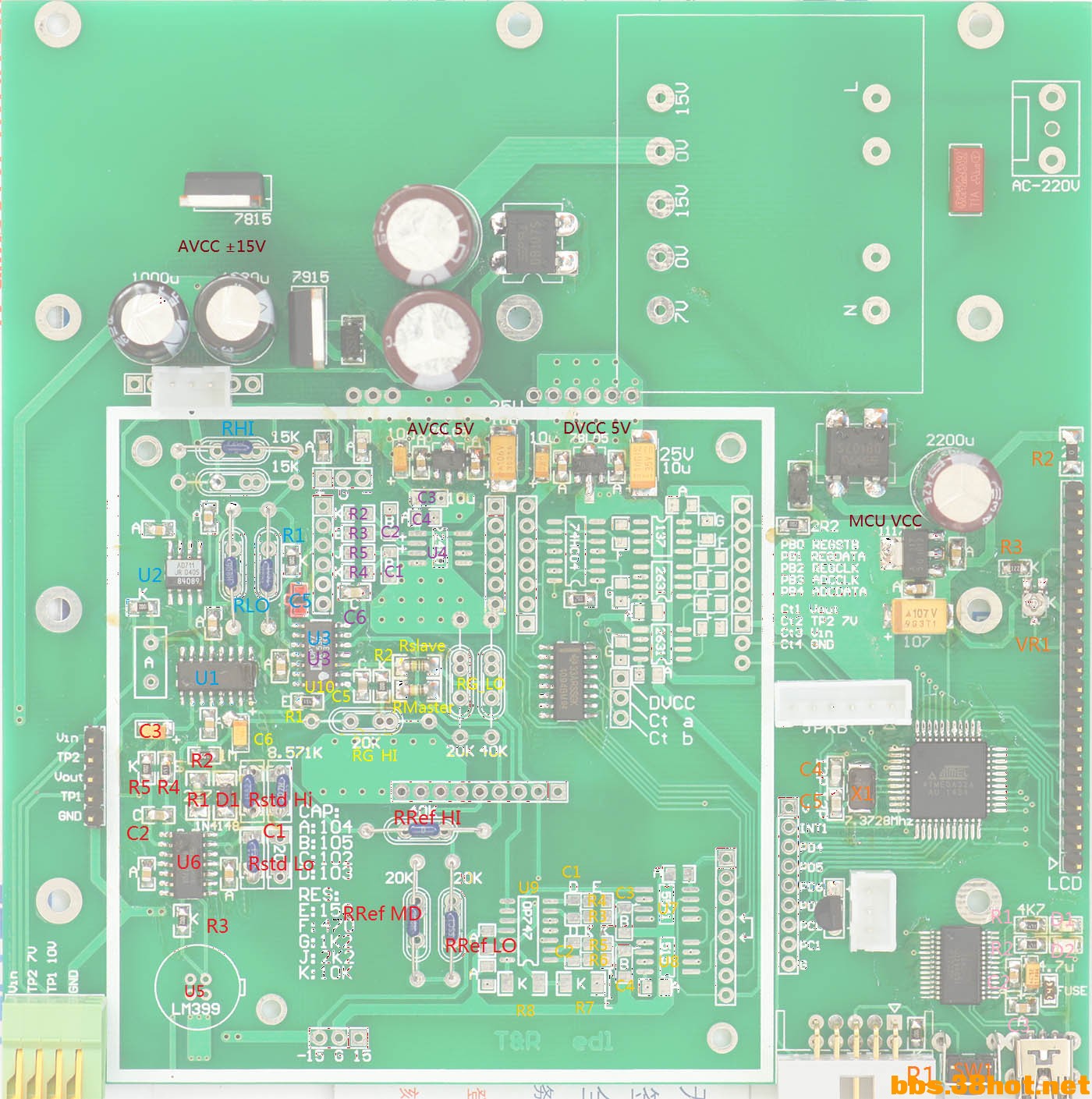

元件索引

详解:

一、模拟部分

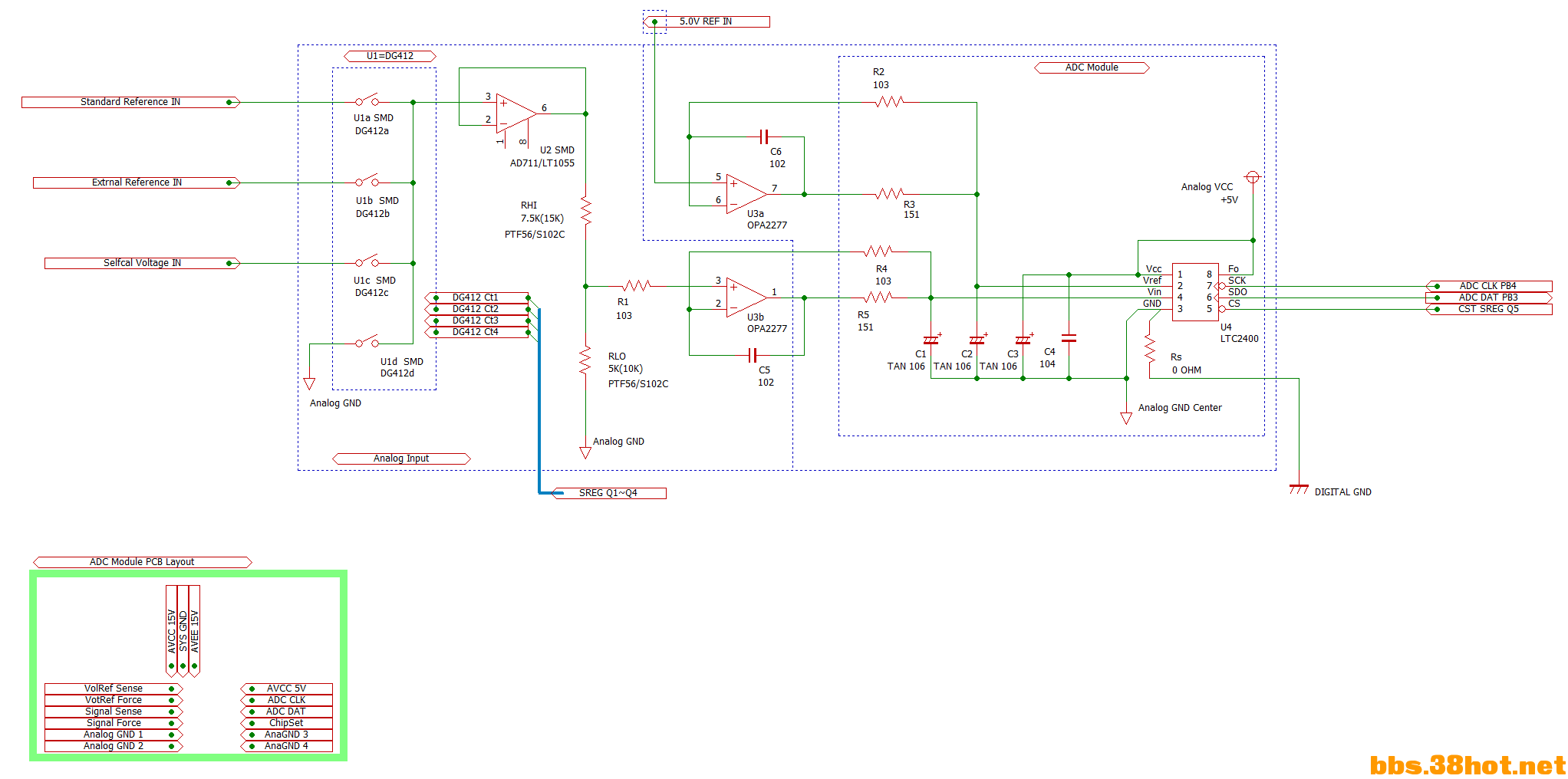

1、输入前端和 ADC,来自电压基准的 7V 和该电压源输出的电压(以及模拟地)经过模拟开关 U1 切换,进入输入前端放大器 U2(V0.1 中,此放大器有 x2.5 和 x10 增益,但在 V0.9 和 V1.0 中画 PCB 的某人嫌麻烦没画),然后进入 x0.4 or x0.2(某人嫌麻烦因此无法通过程序选择,只能根据具体版本更换硬件电路)电路,使得输入信号符合 ADC 输入要求范围。

然后信号进入 U3b 的 ADC 输入驱动器,负责驱动 ADC 的 LTC2400。

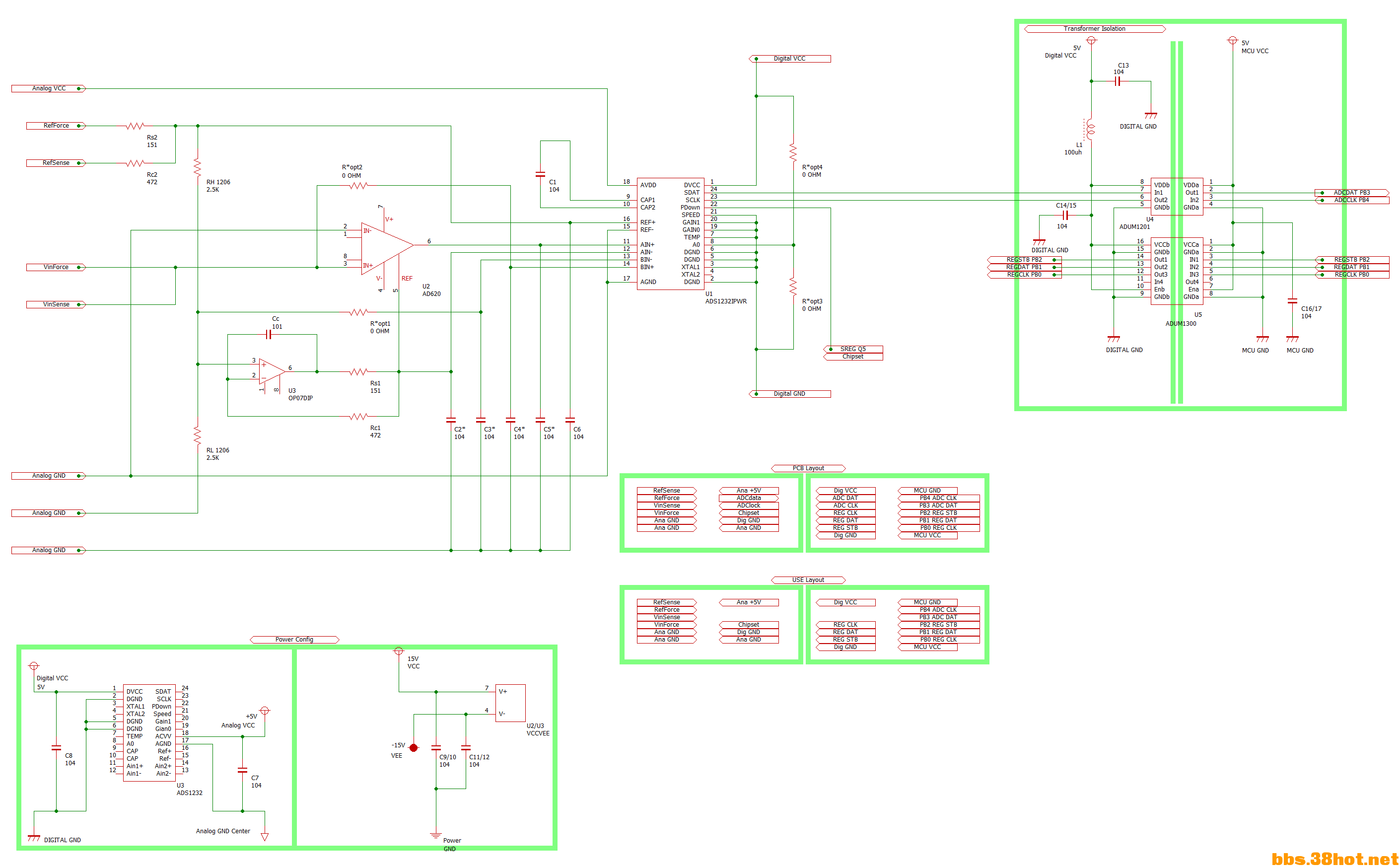

1a、ADC 替换电路之 ADS1232,由于 ADS1232(全差分) 和 LTC2400(非差分)的具体要求差异,在这里用了一片仪放 AD620(INA129)对输入信号进行差分处理以驱动 ADS1232,OP07 负责提供差分偏置。

电路总图

PCB 元件索引

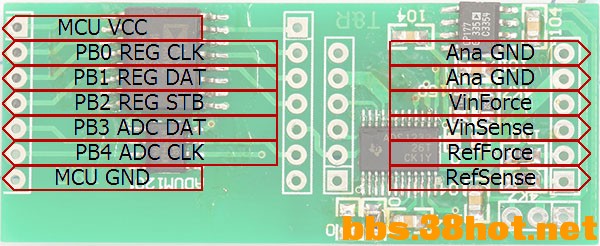

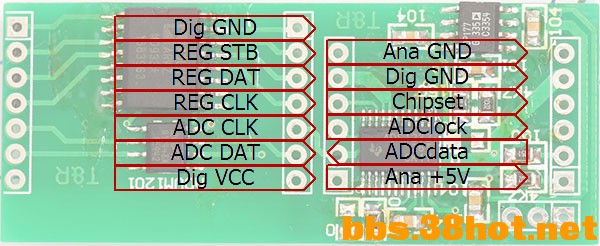

接口配置

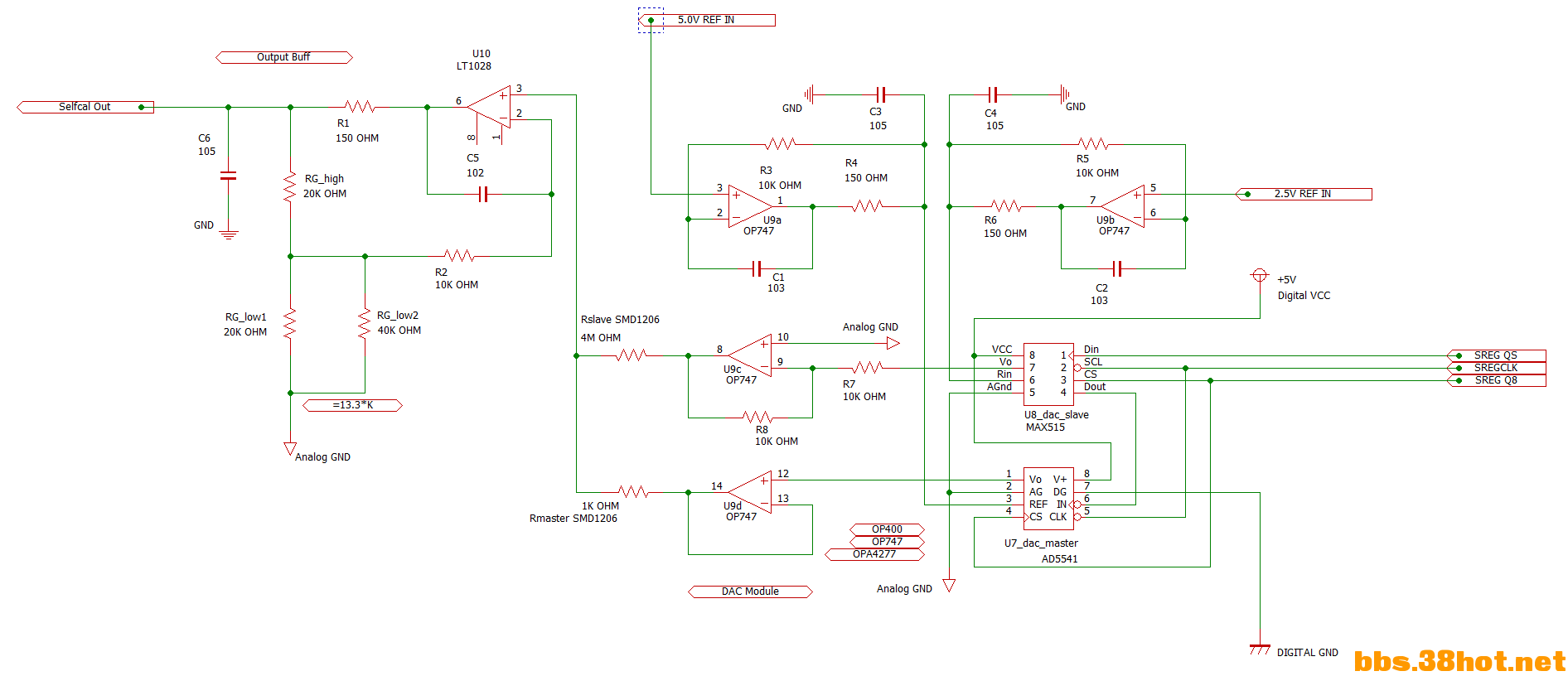

2、DAC 和输出缓冲,经过单片机运算后的数值由 16 位的主 DAC 和 12 位的副 DAC 输出并在缓冲器中合成为一个电压,合成比为 4096:1(约等于 4000:1),因此主 DAC 的有效分辨率降低为 12 位,也就是说主 DAC 可有低 4 位(16LSB)的容差;副 DAC 为 12 位,合成后为 24 位,因此合成后分辨率约为 24 位(16,777,216),相当于 7 位半电压分辨率,设计副 DAC 容差也是低 4 位(16LSB),实际总有效分辨率 20 位(1,048,576),为 6 位半电压分辨率。副 DAC 以负压方式和主 DAC 合成,以实现调零。

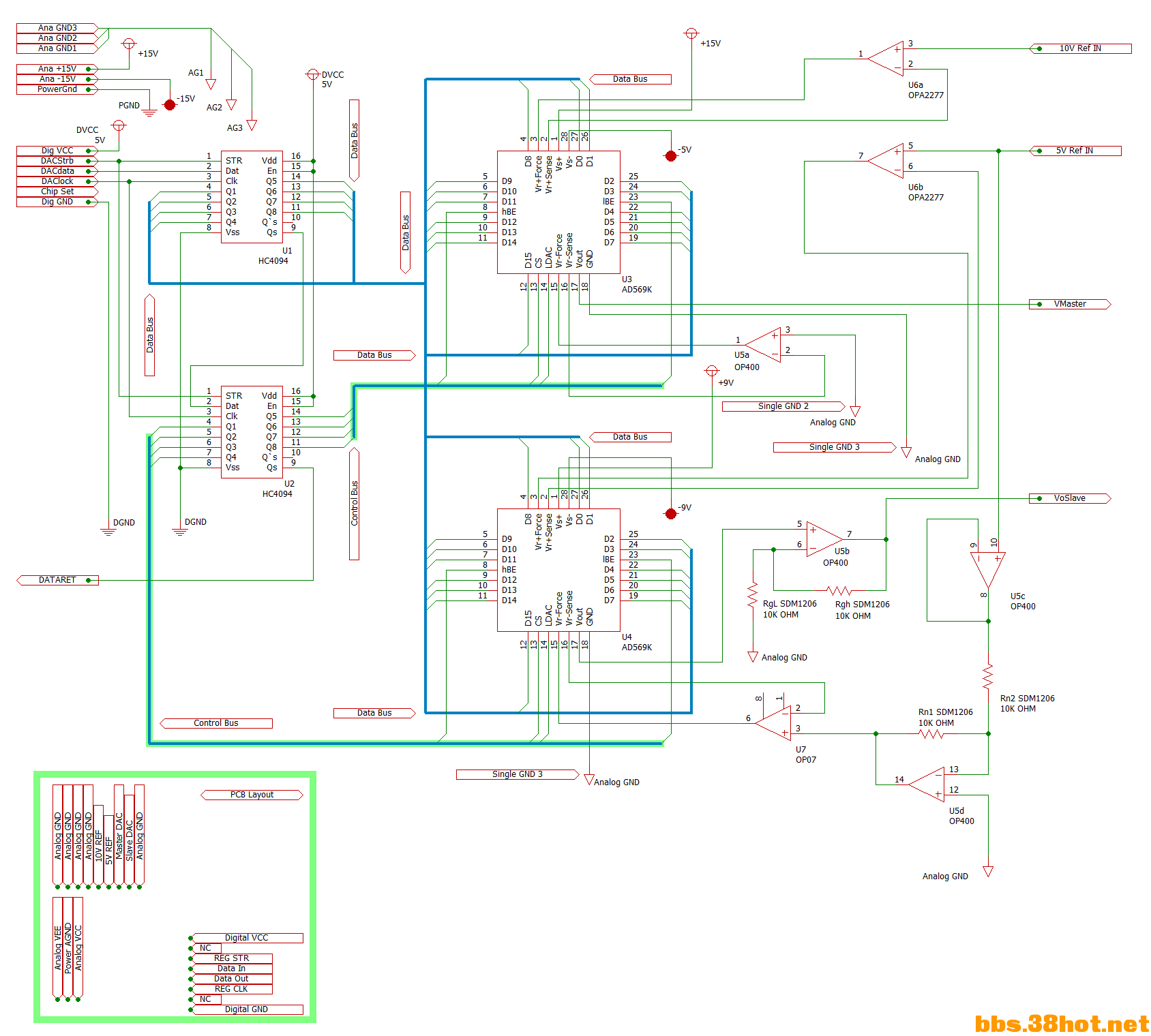

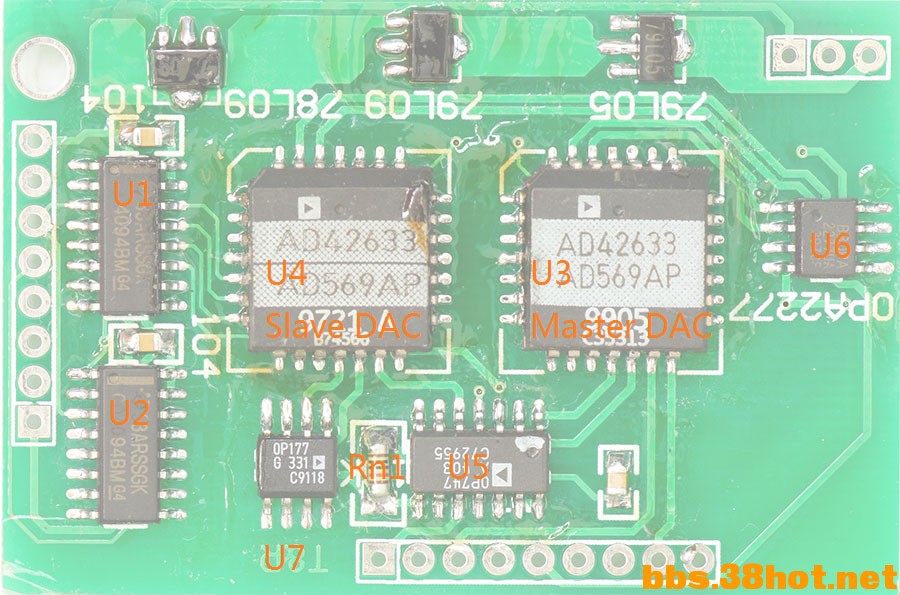

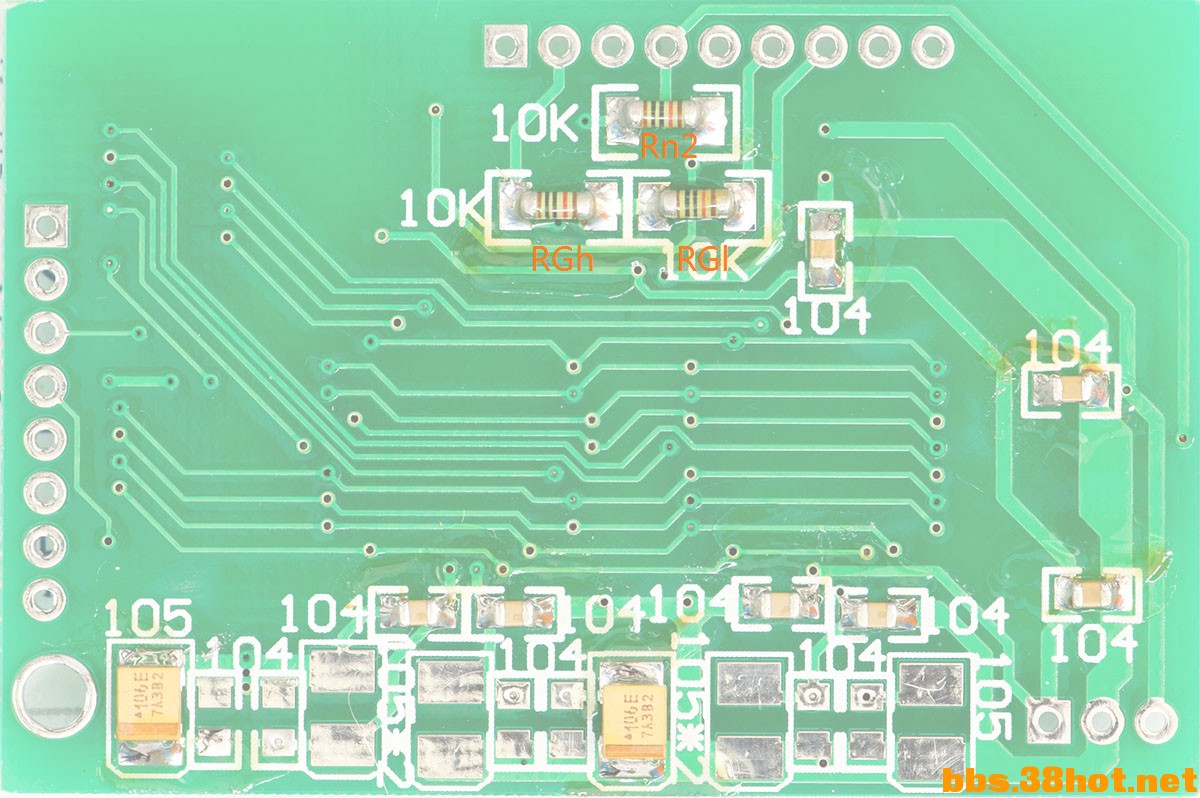

2a、DAC 替换电路之 AD569,由于价格因素,这里用了两片 16 位的 16 位并行总线(可配置为 8 位并行总线) DAC,因此使用两片 CD4094 移位寄存器驱动之;由于 AD569 的具体驱动要求,增加了数片运放以驱动其基准。副 DAC 以正负压方式和主 DAC 合成,以实现调零。

元件索引

接口配置

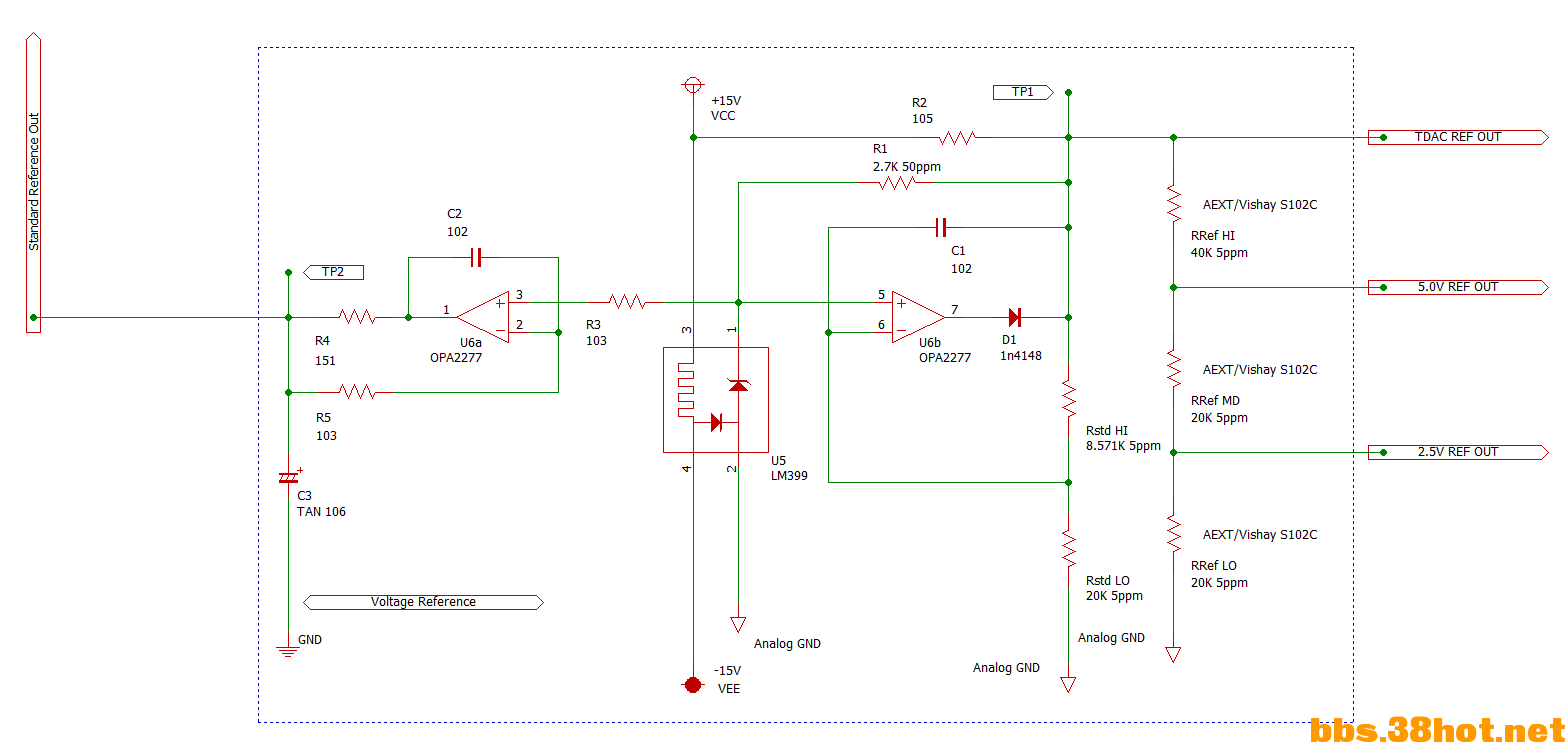

3、电压基准

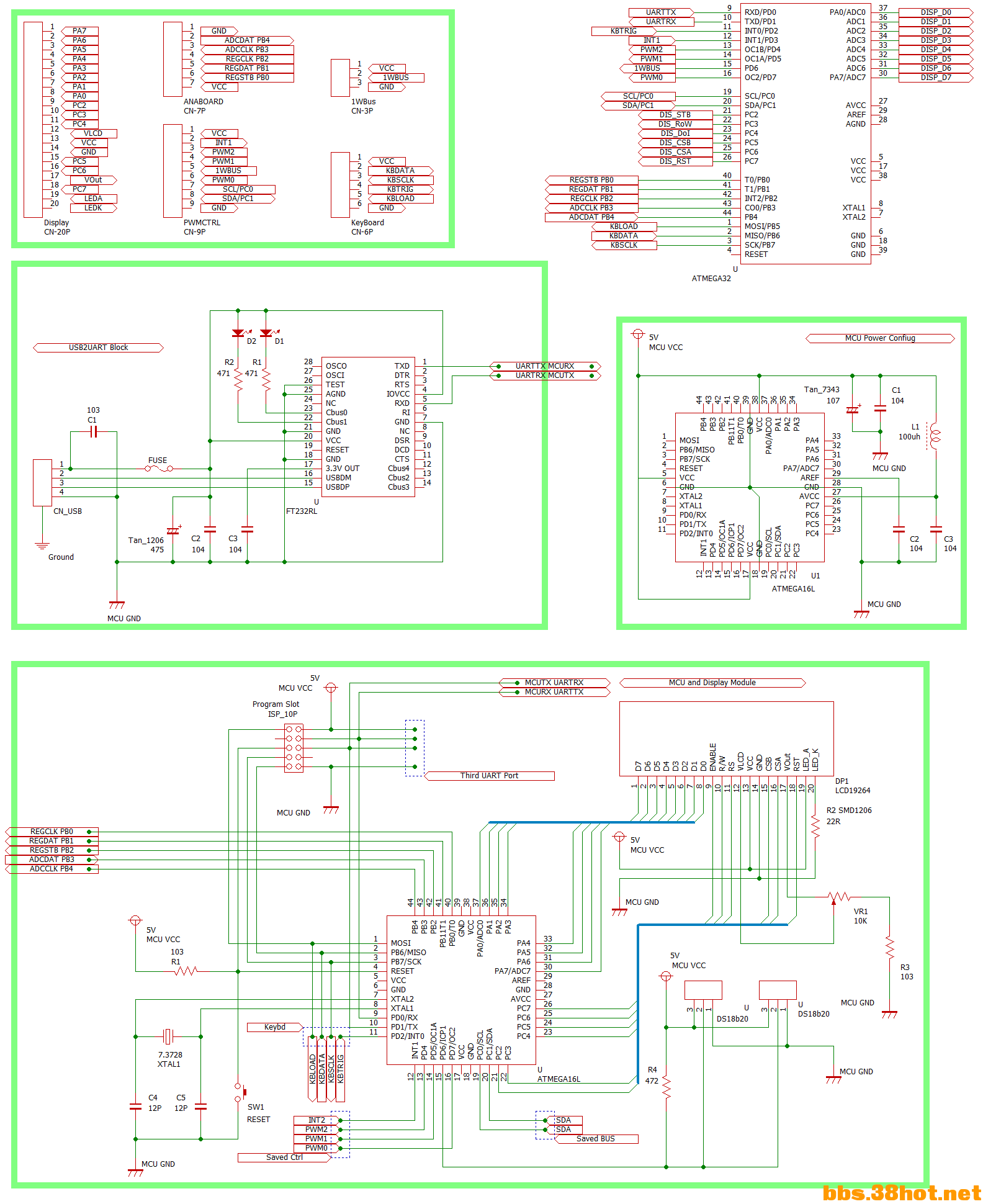

4、数字部分(单片机和 USB 接口)

|